Skystųjų kristalų ekrano LCD ekranas plačiai naudojamas karinėje įrangoje. Ši konstrukcija priima "Spartan-3E FPGA" kaip techninę įrangą. "2 & TImes", 16 simbolių skystųjų kristalų ekranas turi "Sitronix ST7066U" grafinį valdiklį, kad būtų galima suprasti "LCD" ekrano simbolį ar kiną. Visas ekranas, pilno ekrano mobilusis ekranas ir vieno simbolio ekranas. Visos funkcijos yra įdiegtos VHDL kalba, kad atitiktų LCD ekrano reikalavimus ir pasiektų įvairius ekrano efektus.

Dėl mažo dydžio, lengvo svorio ir mažo energijos suvartojimo LCD skystųjų kristalų ekranai turi daugybę pritaikymų. Pavyzdžiui, kaip orlaivių, talpyklų ir laivų ekranų plokštės gali būti sumažintos originalios CRT ekrano vietos, gali sumažėti įrenginio svoris, o mobilumas gali būti padidintas.

Ši konstrukcija naudoja simbolių skystųjų kristalų ekraną su įterptu Si.tronix ST7066U grafiniu valdikliu "Spartan-3E" kūrimo plokšte, kuris įgyvendina: (1) vieno simbolio rodymą bet kurioje pozicijoje ir pilno ekrano bei viso ekrano simbolių rodymą; (2) Individualių simbolių (simbolių) rodymas ir atskirų simbolių pilno ekrano judesio rodymas. Tarp jų grafikos valdiklis [1] yra atsakingas už valdymo komandų ir duomenų priėmimą bei siuntimą į LCD ekraną.

1 Sitronix ST7066U grafikos valdiklis

Valdiklyje yra trys vidinės atmintinės, DD RAM, CGROM ir CG RAM, kurios turėtų būti įjungtos prieš siunčiant duomenis.

(1) DD RAM (disko duomenų atmintis)

Simbolio kodas saugomas. Fiziškai DD RAM turi 80 simbolių poziciją, kiekvienoje eilutėje yra 40 simbolių, tačiau tik 16 gali būti rodomi, o likusios 24 nėra rodomos. Prieš skaitant ar rašydami adreso skaitiklis turi būti inicijuotas. Adreso skaitiklis gali būti laikomas pastovus arba automatiškai padidinamas ar sumažintas 1 po skaitymo ar rašymo.

(2) CG ROM (Character Generator ROM)

Šriftas, kuriame yra kiekvienas iš anksto nustatytas simbolis.

(3) CG RAM (raktų generatoriaus RAM)

Sudėtyje yra 8 bitų pasirinktinių raiškos ženklų. Kiekvienas priskirto simbolio bitas susideda iš 5 taškų 8 bitų bitmape. Konkretus naudojimas yra toks pat kaip DD RAM.

1.1 sąsajos signalai su FPGA

LCD ir FPGA sąsajos signalai [2]: (1) įjungti signalą LCD_E; (2) registruokitės, pasirinkite signalą LCD_RS; (3) skaitymo / rašymo valdymo signalas LCD_RW; (4) keturios LCD duomenų linijos ir StrataFlash duomenų linija SF_D Pakartotinis 11: 8 naudojimas.

1.2 Laiko analizė

SF_D 11: 8, LCD_RS, LCD_RW duomenų reikšmė turi būti nustatyta ir stabili ne mažiau kaip 40 ns, kol LCD_E eina aukštai, o LCD_E išlieka aukšta ne mažiau kaip 230 ns. Daugelyje programų LCD_RW visada yra mažas, nes duomenys paprastai nėra skaitomi iš ekrano.

Kaip parodyta 1 paveiksle, duomenys perduodami 8-bitų formatu ir padalijami į aukštus 4 bitus ir mažus 4 bitus. Pirmieji aukšti 4 bitai, o tada žemieji 4 bitai turi mažiausiai 1u intervalą. 8-bitų rašymo operacija turi būti mažiausiai 40 megabaitų prieš kitą komunikaciją, o po skaidraus komandų vėlavimas turi padidėti iki 1,64 ms.

FPGA LCD LCD dizainas

1 paveiksle pavaizduotas LCD ekrano laiko diagrama

2 duomenų rodymo dizainas

2.1. Srauto diagrama

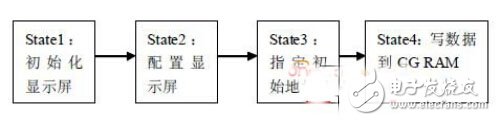

Kaip parodyta 2 paveiksle, LCD duomenų rodinyje yra įjungimo įjungimas, konfigūracijos rodymas, įrašymo duomenys ekrane, o prieš įrašant duomenis reikia nustatyti pradinį adresą.

FPGA LCD LCD dizainas

2 pav. LCD ekrano schema

Plėtros plokštės kristalas yra 50 MHz.